Time synchronisation in programmable device¶

Tomas Martinek (CESNET), Federico Pederzolli (FBK), Joseph Hill (UvA), Mauro Campanella (GARR)

GÉANT INFOSHARE 06 April 2022

www.geant.org

## **Motivation**

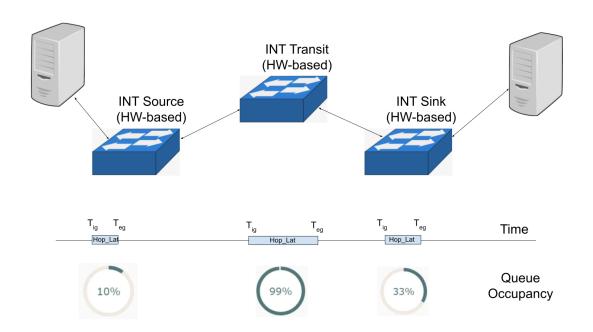

In-band Network Telemetry (INT)

#### Goals

- As part of GN4-3-WP6 research, we are validating various P4 platforms in terms of their ability to implement INT

- One of the key capabilities of INT is to record timestamps of the packet's passage through the switch

- Requirements dependant on the specific use-case:

- One-way Delay (Clock Synchronization)

- Microburst measurements (Timestamp Stability)

- Goal:

- To analyze the capabilities of current P4-programmable platforms in terms of timestamp (TS) recording and clock synchronization (CS)

#### **Platforms tested**

- Software-based

- BMv2

- DPDK: T4P4S, p4c-dpdk

- BPF: p4c-ebpf, p4-xdp, p4c-ubpf

- SmartNIC-based

- NetFPGA

- Netcope P4

- Netronome

- Hardware switch

- Intel Tofino

## **Major Findings**

- Timestamp support

- Some platforms do not support timestamps at all

- T4P4S, p4c-dpdk, p4c-ebpf

- Timestamp format, range and meaning

| Platform   | Resolution<br>[bits] | Meaning                                                             | Epoch                    |

|------------|----------------------|---------------------------------------------------------------------|--------------------------|

| BMv2       | 48                   | Number of microseconds                                              | Switch start             |

| Tofino v1  | 48                   | Number of nanoseconds                                               | Adjustable               |

| Netcope P4 | 64                   | Number of nanoseconds                                               | Adjustable               |

| NetFPGA    | 64                   | Number of units derived from the clock signal source (8ns or 6.4ns) | Since the FPGA boot time |

## **Major Findings**

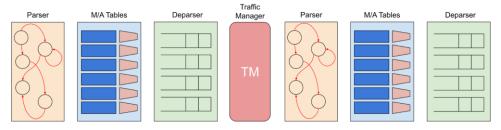

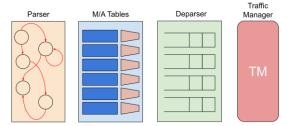

#### Impact of P4 architecture used

- TS recorded during transition between PHY and MAC (Tofino, Netcope, Netronome)

- TS recorded when entering the ingress and egress pipeline (Tofino)

- TS obtained by calling extern (NetFPGA, Netronome)

- Some of the architectures have ingress pipeline only (NetFPGA, Netcope)

**PSA Architecture**

SimpleSumeSwitch Architecture

## **Major Findings**

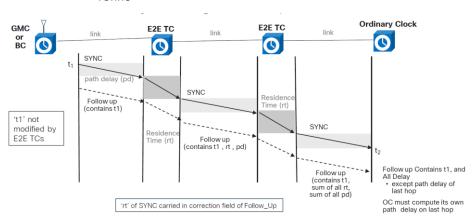

- Clock Synchronization

- No synchronization

- NetFPGA

- Network Time Protocol (NTP) accuracy in orders of milliseconds, software-based approach

- Netcope P4

- Precise Time Protocol (PTP) sub-microsecond accuracy, hardware support required

- NIC (ptp4lin, phc2sys)

- Tofino

#### PTP switch:

- Calculates residence time

- Updates correctionField in PTP packet

P4-based switches can help in significant expansion of PTP in the near future

### **Conclusions**

- Existing platforms vary considerably

- Support for TS, format, range, location where the TS is recorded

- Software-based platforms

- TS and CS not implemented or used from the system time

- Measurement accuracy affected by software layer overhead

- DPDK-based platforms are the most promising (T4P4S)

- Hardware-based platforms

- TS and CS implemented (NTP, PTP, PPS)

- Tofino represents the best production quality platform

- More detailed information is part of the White Paper, which will be coming soon

# Thank you

Any questions?

gn4-3-wp6-t1-dpp@lists.geant.org int-discuss@lists.geant.org

www.geant.org

© GÉANT Association on behalf of the GN4 Phase 3 project

The research leading to these results has received funding

the European Union's Horizon 2020 research and innovation programme under Grant Agreement No. 856726 (GN4-3).